|                        | tecture                                   |      |

|------------------------|-------------------------------------------|------|

|                        |                                           |      |

|                        |                                           |      |

|                        |                                           |      |

|                        |                                           |      |

|                        |                                           |      |

|                        |                                           |      |

|                        | Sistemas de Computação                    |      |

|                        |                                           |      |

|                        | Sétima Aula                               |      |

|                        |                                           |      |

|                        |                                           |      |

|                        | Haroldo Gambini Santos                    |      |

|                        |                                           |      |

|                        | Universidade Federal de Ouro Preto - UFOP |      |

|                        | 0.1 1.1.0000                              |      |

|                        | 3 de setembro de 2009                     |      |

|                        |                                           |      |

|                        |                                           |      |

|                        |                                           |      |

|                        |                                           |      |

|                        |                                           |      |

| Iaroldo Gambini Santos | Sistemas de Computação                    | 1/20 |

|                        |                                           |      |

| Notas |  |  |  |

|-------|--|--|--|

| -     |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

| Seção                   |              |  |

|-------------------------|--------------|--|

|                         |              |  |

|                         |              |  |

|                         |              |  |

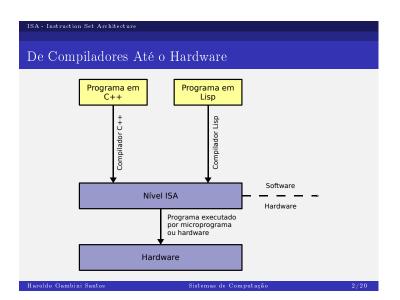

| 1 ISA - Instruction Set | Architecture |  |

|                         |              |  |

|                         |              |  |

|                         |              |  |

| Notas |  |  |  |

|-------|--|--|--|

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

| Votas |  |  |  |

|-------|--|--|--|

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

| ■ Instruções são números (grupamento de 0 ´s e 1 ´s)                                 |  |

|--------------------------------------------------------------------------------------|--|

| Instruções são compostas por 2 tipos de campos a saber:                              |  |

| OP CODE código da instrução. Indica o que a ALU irá<br>fazer (soma, subtração, etc.) |  |

| Operando(s) indica a CPU com que dados a CPU realizará                               |  |

| a operação (podem ser endereços ou mesmo                                             |  |

| $\operatorname{valores})$                                                            |  |

| ■ 1 OP CODE por instrução                                                            |  |

| ■ 0 ou mais operandos por instrução                                                  |  |

|                                                                                      |  |

|                                                                                      |  |

| Sambini Santos Sistemas de Computação 3/20                                           |  |

|                                                                                      |  |

|                                                                                      |  |

${\rm Not\,as}$

| ISA - Instruction Set Architect | ure                                           |      |

|---------------------------------|-----------------------------------------------|------|

|                                 |                                               |      |

| Mnemônicos                      |                                               |      |

|                                 |                                               |      |

| ■ codificação d                 | le instruções para facilitar o programador na |      |

| tarefa de esc                   | rever código de baixo nível                   |      |

| ■ ao invés de 0<br>■ ADD, A, B, | 01010001110101000101000111010100              |      |

| ■ RDD , R , D ,                 |                                               |      |

|                                 |                                               |      |

|                                 |                                               |      |

|                                 |                                               |      |

| Haroldo Gambini Santos          | Sistemas de Computação                        | 4/20 |

ISA - Instruction Set Architecture Endereços mais curtos Hexadecimal  $\blacksquare$ também chamado base-16, hexa ou hex ■ símbolos: {0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F} ■ representação mais amigável de valores binários  $\blacksquare$ cada letra representa um  $\it nibble$  (4 bits) ■ exemplo: 0110101100001101111110000110001010

em hex: 6B0DF18A

| Notas |  |  |  |

|-------|--|--|--|

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

| ISA - Instruction Set Architecture                                                                                 |       |

|--------------------------------------------------------------------------------------------------------------------|-------|

| Representação de Instruções                                                                                        | Notas |

| Instruções sem operandos                                                                                           |       |

| ■ RESET<br>■ NOP                                                                                                   |       |

| ■                                                                                                                  |       |

| Instruções com 1 operando  ■ ADD A (ACC = ACC + A)                                                                 |       |

| ■                                                                                                                  |       |

| Haroldo Gambini Santos Sistemas de Computação 6/20                                                                 |       |

|                                                                                                                    |       |

|                                                                                                                    |       |

| ISA - Instruction Set Architecture                                                                                 |       |

| Representação de Instruções                                                                                        | Notas |

| Instruções com 2 operandos                                                                                         |       |

| lacksquare ADD A, B $(A=A+B)$                                                                                      |       |

| $\label{eq:bounds} \begin{array}{ll} \blacksquare \mbox{ MOVE A, B}  (A=B) \\ \\ \blacksquare  \ldots \end{array}$ |       |

| Instruções com 3 operandos                                                                                         |       |

| $=$ ADD A D C (A D $\perp$ C)                                                                                      |       |

| $\blacksquare$ ADD A, B, C $(A=B+C)$ $\blacksquare$ MUL A, B, C $(A=B\times C)$                                    |       |

| lacktriangledown MUL A, B, C $(A=B	imes C)$                                                                        |       |

|                                                                                                                    |       |

| lacktriangledown MUL A, B, C $(A=B	imes C)$                                                                        |       |

| lacktriangledown MUL A, B, C $(A=B	imes C)$                                                                        |       |

Representação de Instruções

Instruções com 4 operandos

ADD A, B, C, O4h (A = B + C, próx. instr. em 04h)

...

...

Notas

| ISA - Instruction Set Architecture                                                                    |       |

|-------------------------------------------------------------------------------------------------------|-------|

| Arquitetura de um computador                                                                          | Notas |

|                                                                                                       |       |

|                                                                                                       |       |

| ■ CPU: caminho de dados + controle                                                                    |       |

| <ul> <li>Organização da memória</li> </ul>                                                            |       |

| <ul> <li>Conjunto de instruções básicas</li> <li>pontos de vista: Projetista × Programador</li> </ul> |       |

| <ul> <li>instruções, registradores e endereços de memória são<br/>números</li> </ul>                  |       |

|                                                                                                       |       |

|                                                                                                       |       |

|                                                                                                       |       |

| Haroldo Gambini Santos Sistemas de Computação 9/20                                                    |       |

|                                                                                                       |       |

|                                                                                                       |       |

|                                                                                                       |       |

|                                                                                                       |       |

| ISA - Instruction Set Architecture                                                                    |       |

| TO A                                                                                                  | Notas |

| ISA                                                                                                   | 10045 |

|                                                                                                       |       |

| Instruction Set Architecture                                                                          |       |

| <ul> <li>descreve os aspectos da arquitetura do computador,<br/>"visíveis" ao programador</li> </ul>  |       |

| Aspectos considerados:                                                                                |       |

| ■ tipos primitivos de dados<br>■ instruções                                                           |       |

| ■ número de operandos<br>■ registradores (tipos e forma de acesso)                                    |       |

| $\blacksquare$ forma de endereçamento (acesso) à memória $\blacksquare$                               |       |

|                                                                                                       |       |

|                                                                                                       |       |

| Haroldo Gambini Santos Sistemas de Computação 10/20                                                   |       |

|                                                                                                       |       |

|                                                                                                       |       |

ISAInstruction Set Architecture ■ inclui todos os comandos capazes de serem reconhecidos

- pelo projeto de uma CPU

- esses comandos são instruções

- cada instrução possui um OP CODE próprio

- o conjunto dessas instruções (OP CODES) de cada CPU forma o que chamamos de linguagem de máquina da CPU. (assembly)

${\rm Not\,as}$

| ISA - Instruction Set Architecture                                                                                                                                                                                         |        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| ISA : Decisões importantes                                                                                                                                                                                                 | Not as |

| <ul> <li>operações</li> <li>quantas</li> <li>operandos</li> <li>quantos</li> <li>localização</li> <li>tipos</li> <li>como especificar</li> <li>formato de instruções</li> <li>tamanho</li> <li>quantos formatos</li> </ul> |        |

| Haroldo Gambini Santos Sistemas de Computação 12/20                                                                                                                                                                        |        |

|                                                                                                                                                                                                                            |        |

| ISA - Instruction Set Architecture                                                                                                                                                                                         |        |

| ISA                                                                                                                                                                                                                        | Notas  |

| Localização de Operadores                                                                                                                                                                                                  |        |

| <ul><li>Acumulador</li><li>Pilha</li></ul>                                                                                                                                                                                 |        |

| ■ Registradores                                                                                                                                                                                                            |        |

| <ul><li>Memória</li><li>Tipos comuns de máquinas:</li></ul>                                                                                                                                                                |        |

| ■ acumulador ■ pilha ■ registrador memório                                                                                                                                                                                 |        |

| ■ registrador-memória<br>■ load-store                                                                                                                                                                                      |        |

| Haroldo Gambini Santos Sistemas de Computação 13/20                                                                                                                                                                        |        |

| naronio Gambini Santos Sistemas de Computação 15/20                                                                                                                                                                        |        |

|                                                                                                                                                                                                                            |        |

|                                                                                                                                                                                                                            |        |

| ISA - Instruction Set Architecture                                                                                                                                                                                         |        |

| ISA                                                                                                                                                                                                                        | Notas  |

Haroldo Gambini Santos Sistemas de Compu

■ General Purpose Register

lacksquare 1 endereço: ADD A (acc  $\leftarrow$  acc + mem[A])

■ 0 endereços: ADD ( $tos \leftarrow tos + next$ )

$\begin{array}{c} \blacksquare \ 2 \ \text{enderecos: ADD A B} \ (A \leftarrow A + B) \\ \blacksquare \ 3 \ \text{enderecos: ADD A B} \ (A \leftarrow B + C) \\ \end{array}$

Quantos operandos

• Acumulador

■ Pilha

14/

| ISA - I | struction Set Architecture                                            |                                                                                                     |  |  |  |  |  |

|---------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         |                                                                       |                                                                                                     |  |  |  |  |  |

| ISA     |                                                                       |                                                                                                     |  |  |  |  |  |

|         |                                                                       |                                                                                                     |  |  |  |  |  |

|         | Acumulador Simp                                                       | oles(EDSAC 1950)                                                                                    |  |  |  |  |  |

|         | Accumulator +Index Registers (Manchester Mark I, IBM 700 series 1953) |                                                                                                     |  |  |  |  |  |

|         | Separação do Modelo de Pr <b>g</b> ramação<br>da Implementação        |                                                                                                     |  |  |  |  |  |

|         | Baseado em Linguagens<br>de Alto Nível<br>(B5000 1963)                | Conceito de Família<br>(IBM 360 1964)                                                               |  |  |  |  |  |

|         | General Purpose                                                       | Register Machines                                                                                   |  |  |  |  |  |

|         | Complex Instruction Sets<br>(Vax, Intel 432 1977-80)                  | Load/Store Architecture<br>(CDC 6600, Cray 1 1963-76)<br>RISC<br>(Mips,Sparc,88000,IBM RS6000,1987) |  |  |  |  |  |

| Notas |  |  |  |

|-------|--|--|--|

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

ISA - Instruction Set Architecture

## ISA - Classes

#### Acumulador

Vantagens minimiza os estados na máquina; instruções curtas Desvantagens acumulador é o único local de armazenamento temporário - icorre em uma comunicação maior com a memória

#### Pilha

Vantagens instruções curtas; avaliação fácil de expressões

Desvantagens pilha não pode ser acessada aleatóriamente difícil de se gerar código eficiente; implementação

eficiente também difícil

Haroldo Gambini Santos

Sistemas de Computação

16/20

${\rm Not}\, as$

ISA - Instruction Set Architecture

## ISA - Classes

### Registradores

Vantagem modelo mais geral para geração de código Desvantagem todos os operandos precisam ser nomeados, o que gera instruções mais longas

- $\blacksquare$ registradores são mais rápidos do que a memória

- registradores são mais fáceis para o compilador utilizar

- registradores podem ser utilizados mais eficientemente do que outras formas de armazenamento interno

| ISA - | Instruction | Set | Architecture |

|-------|-------------|-----|--------------|

|       |             |     |              |

# ISA

### Operações comuns

lógicas e aritméticas soma, E, diferença, OU

transferência de dados loads/stores

controle branch, jump, ...

sistema gerenciamento de cache, memória virtual, ...

ponto flutuante operações de PF: soma, multiplicação,...

string operações em cadeias de caracteres: mover,

comparar, buscar,...

| roldo |  |  |

|-------|--|--|

|       |  |  |

Sistemas de Computação

18/20

| Notas |  |  |

|-------|--|--|

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

|       |  |  |

#### ISA - Instruction Set Architectur

# ISA

| posição | instrução              | % perc. execuções |

|---------|------------------------|-------------------|

| 1       | load                   | 22,00%            |

| 2       | conditional branch     | $20,\!00\%$       |

| 3       | compare                | $16,\!00\%$       |

| 4       | store                  | 12,00%            |

| 5       | add                    | $8{,}00\%$        |

| 6       | and                    | $6{,}00\%$        |

| 7       | sub                    | $5{,}00\%$        |

| 8       | move register-register | $4{,}00\%$        |

| 9       | call                   | 1,00%             |

| 10      | return                 | 1,00%             |

total: 96%

Haroldo Gambini Santo

Sistemas de Computação

19/20

ISA - Instruction Set Architecture

| Notas |  |  |  |

|-------|--|--|--|

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |