# Sistemas de Computação Sexta Aula

Haroldo Gambini Santos

Universidade Federal de Ouro Preto - UFOP

15 de abril de 2010

# Seção

1 A Memória Principal

2 Outros Tipos de Memória

3 Chips e Barramento de CPU

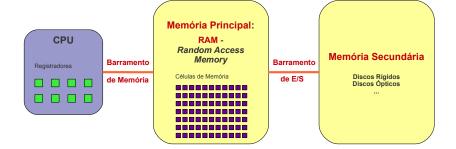

# A Memória Principal

### RAM: Random Access Memory

Memória de Acesso Aleatório: o custo de acessar uma célula da memória não depende da posição da mesma (ao contrário da memória de acesso seqüencial).

### História

## Memória de Núcleo Magnético - Core Memory

- forma mais comum de armazenamento de acesso aleatório nos primeiros computadores;

- empregava uma matriz de anéis ferromagnéticos;

- tornou-se obsoleta com a chegada das memórias semicondutoras;

- nome deu origem a expressões ainda usadas ex: core dump.

# Memória Principal Semicondutora

## DRAM - RAM Dinâmica

■ Elementos para 1 bit:

C capacitor

M transistor

AL linha de acesso

DL linha de dados

- O valor é armazenado como carga no capacitor

- há necessidade de recarga períodica do mesmo, o que implica ciclos de "refresh".

- Leitura:

- linha de acesso conecta

- corrente flui ou n\u00e3o para linha de dados, dependendo do estado do capacitor

## Tipos de RAMs

#### Estáticas - SRAMs

■ Implementadas com flip-flops (≥ 6 transistores por bit!, menos densa)

### Dinâmicas - DRAMs

■ 1 transistor e um capacitor por bit - alta densidade!

## Tipos de RAMs

#### Estáticas - SRAMs

- Implementadas com flip-flops (≥ 6 transistores por bit!, menos densa)

- Estáveis (guarda o valor enquanto houver energia

### Dinâmicas - DRAMs

- 1 transistor e um capacitor por bit - alta densidade!

- Instável: necessidade de renovação da carga

# Tipos de RAMs

### Estáticas - SRAMs

- Implementadas com flip-flops (≥ 6 transistores por bit!, menos densa)

- Estáveis (guarda o valor enquanto houver energia

- Rápida

- Usada comummente em cache nível 2

#### Dinâmicas - DRAMs

- 1 transistor e um capacitor por bit - alta densidade!

- Instável: necessidade de renovação da carga

- Mais lenta

# Seção

1 A Memória Principal

2 Outros Tipos de Memória

3 Chips e Barramento de CPU

# ROMs - Read Only Memories (mem. somente de leitura)

- Dados gravados no processo de fabricação

- Baratas quando produzidas em grande quantidade

## ROMs - Mais flexibilidade

## PROM - Programmable ROM

Pode ser programada uma vez em campo

## ROMs - Mais flexibilidade

## PROM - Programmable ROM

Pode ser programada uma vez em campo

### EPROM - Erasable PROM

- Pode ser programada e apagada em campo

- Exposição a luz ultravioleta

## ROMs - Mais flexibilidade

## PROM - Programmable ROM

Pode ser programada uma vez em campo

### EPROM - Erasable PROM

- Pode ser programada e apagada em campo

- Exposição a luz ultravioleta

#### **EEPROM**

- Programada por pulsos

- Muito mais lentas que DRAMs ou SRAMS

## EEPROM - Memória Flash

# Seção

1 A Memória Principal

2 Outros Tipos de Memória

3 Chips e Barramento de CPU

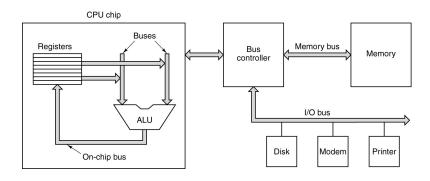

## CPUs Modernas

■ Contidas em 1 só chip (VLSI)

## CPUs Modernas

- Contidas em 1 só chip (VLSI)

- Interage com

- Memória

- Dispositivos de E/S

## CPUs Modernas

- Contidas em 1 só chip (VLSI)

- Interage com

- Memória

- Dispositivos de E/S

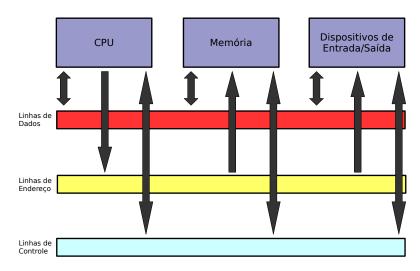

- Comunica através dos **pinos** utilizando um **barramento**

## Pinos

- Endereço

- Dados

- Controle

- Energia

- Busca de uma instrução:

- I CPU coloca endeço da instrução nos pinos de endereço

- Busca de uma instrução:

- 1 CPU coloca endeço da instrução nos pinos de endereço

- 2 ativa linhas de controle para informar que quer buscar algo da memória.

- Busca de uma instrução:

- 1 CPU coloca endeço da instrução nos pinos de endereço

- 2 ativa linhas de controle para informar que quer buscar algo da memória

- 3 memória responde colocando valor nos pinos de dados

- Busca de uma instrução:

- 1 CPU coloca endeço da instrução nos pinos de endereço

- 2 ativa linhas de controle para informar que quer buscar algo da memória

- 3 memória responde colocando valor nos pinos de dados

- 4 memória ativa sinal indicando a conclusão da tarefa

- Busca de uma instrução:

- I CPU coloca endeço da instrução nos pinos de endereço

- 2 ativa linhas de controle para informar que quer buscar algo da memória

- 3 memória responde colocando valor nos pinos de dados

- 4 memória ativa sinal indicando a conclusão da tarefa

- 5 CPU recebe palavra e executa a instrução

# Pinos dos Chips da CPU

### Pinos de Endereço e Dados

- Críticos para o desempenho da CPU

- Pinos de endereço

- $\blacksquare$  m pinos:  $2^m$  locacalizações de memória endereçáveis

- $\blacksquare$  valores típicos de m: 16, 20, 32 e 64

- Pinos de dados

- $\blacksquare$  *n* pinos de dados: leitura de *n* bits por vez

- valores típicos de n: 8, 16, 32, 36 e 64

## Protocolo de Barramento

- Especificações

- mecânicas

- elétricas

- temporizações

- ..

#### Protocolo de Barramento

- Especificações

- mecânicas

- elétricas

- temporizações

- ..

- Exemplos:

- Unibus (PDP-11)

- ISA (PC-AT)

- PCI (comum em PCs)

- USB Universal Serial Bus (PCs modernos)

- ...

# Dispositivos

### Tipos

Mestres : dispositivos que podem iniciar transferências no

barramento

Escravos : dispositivos que aguardam requisições

Transceptor: dispositivo que age como os dois